|

SH |

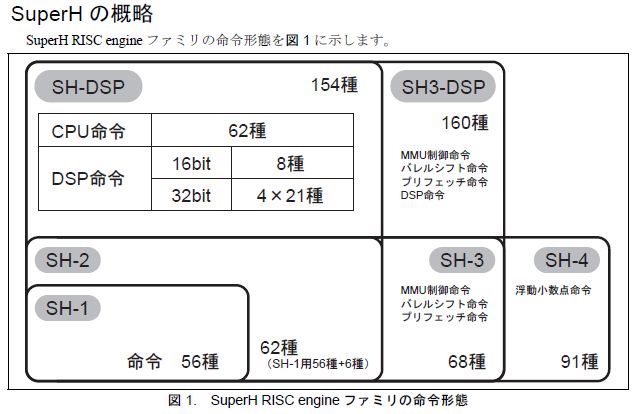

ルネサス社の32ビットの RISC のプロセッサです。 SHは SuperH RISC engine の略です、ファミリを示すためにソフトウェアマニュアルから下の図を引用します。

| 図1: ファミリ概要 |

|

RISC

のプロセッサは固定長の命令形式を採用しており命令解析の論理がスッキリしたものになります。

本ファミリのチップは周辺機能を備えたマイクロコントローラとして供給されています。

MMUやDSPの機能を持つものもありますが当サイトの注目しているのはプロセッサのコア部分であり

ファミリで言えば

SH-1,SH-2,SH-4

です。

|

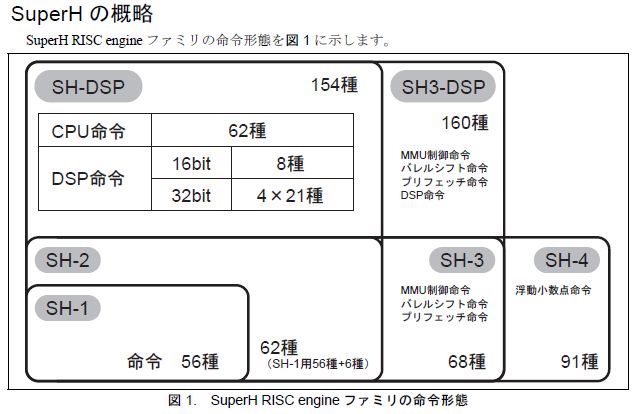

汎用レジスタ |

| 図2: 汎用レジスタ |

|

SHプロセッサは32ビットの汎用レジスタを16個持っています。

R15

はスタックポインタと兼用されています。

RISC

のプロセッサの特徴は多数の汎用レジスタを持ち基本的に専用のレジスタを置きません。

レジスタの構造をひとつだけ持ち記憶本体は選択するだけなので論理を少なくすることができます。

|

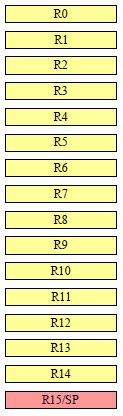

ステータスレジスタ |

| 図3: ステータスレジスタ |

|

|

システムレジスタ |

|

積和レジスタ |

| 図5: 積和レジスタ |

|

積和演算の結果を格納します。

|

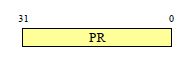

プロシージャレジスタ |

| 図6: プロシージャレジスタ |

|

サブルーチンプロシージャからの戻り先アドレスの格納レ ジスタです。

|

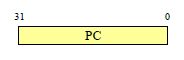

プログラムカウンタ |

| 図7: プログラムカウンタ |

|

PCは現在実行中の命令の2バイト(2命令)先を示してい ます。

|

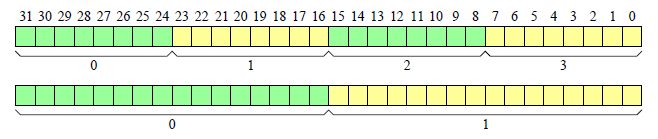

データ構造 |

SHプロセッサ のデータ構造は 80x86 とは違っています、より速度が向上して プロセッサ の論理設計も単純になったと思います。 すなわち16ビットのデータも扱えるが32ビットの境界をまたがないようになっています。 80x86 では全てのデータ位置を8ビット境界においていたのでプロセッサのメモリ操作が複雑になっていました。

| 図4: 8/16ビットデータの配置 |

|

番地の配置は小さい番地が上位のビットから占めていくビックエンディアンです。

|

命令セット |

SHマイコンの命令は固定長の16ビットです。

|

ADD Rm,Rn |

汎用レジスタの Rm と Rn の値を加算して結果を Rn に記憶します。

| 命令符 | |||||||||||||||

| 0 | 0 | 1 | 1 | n | n | n | n | m | m | m | m | 1 | 1 | 0 | 0 |

|

ADD #imm,Rn |

汎用レジスタの Rn と 8ビットの即値の i を加算して結果を Rn に記憶します。

| 命令符 | |||||||||||||||

| 0 | 1 | 1 | 1 | n | n | n | n | i | i | i | i | i | i | i | i |

|

ADDC Rm,Rn |

汎用レジスタ Rn の値と Rm の値と T ビットの値を加算して結果を Rn に記憶します。 加算によるビット31からの桁上がりは T ビットに記憶します。

| 命令符 | |||||||||||||||

| 0 | 0 | 1 | 1 | n | n | n | n | m | m | m | m | 1 | 1 | 1 | 0 |

|

ADDV Rm,Rn |

汎用レジスタ Rn の値と Rm の値を加算して結果を Rn に記憶します。 レジスタ値を符号付整数として加算結果が正負のどちらかを超えた場合は T ビットに 1 を記憶します。

| 命令符 | |||||||||||||||

| 0 | 0 | 1 | 1 | n | n | n | n | m | m | m | m | 1 | 1 | 1 | 1 |

|

AND Rm,Rn |

汎用レジスタ Rn の値と Rm の値を論理積して Rn に記憶します。

| 命令符 | |||||||||||||||

| 0 | 0 | 1 | 0 | n | n | n | n | m | m | m | m | 1 | 0 | 0 | 1 |

|

AND #imm,R0 |

汎用レジスタの R0 と 8ビットの即値の i を論理積して結果を R0 に記憶します。

| 命令符 | |||||||||||||||

| 1 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | i | i | i | i | i | i | i | i |

|

AND #imm,@(R0,GBR) |

汎用レジスタの R0 と GBR の加算値を番地にしたメモリの8ビット値と 8ビットの即値の i を論理積して結果を R0 と GBR の加算値を番地にしたメモリに8ビットで書き込みます。

| 命令符 | |||||||||||||||

| 1 | 1 | 0 | 0 | 1 | 1 | 0 | 1 | i | i | i | i | i | i | i | i |

|

BF label |

ステータスレジスタのビット T が0のときに分岐する命令です。 本命令から4バイト後のプログラムカウンタ値に符号付の8ビット値を2倍して加算する相対分岐です。

| 命令符 | |||||||||||||||

| 1 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | d | d | d | d | d | d | d | d |

|

BF/S label |

ステータスレジスタのビット

T

が0のときに分岐する命令です。

本命令から4バイト後のプログラムカウンタ値に符号付の8ビット値を2倍して加算する相対分岐です。

本命令は遅延分岐しますので先に遅延スロットの命令を実行します。

遅延スロットの命令が分岐命令であってはなりません。

| 命令符 | |||||||||||||||

| 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | d | d | d | d | d | d | d | d |

|

BRA label |

無条件分岐命令です。

本命令から4バイト後のプログラムカウンタ値に符号付の12ビット値を2倍して加算する相対分岐です。

本命令は遅延分岐しますので先に遅延スロットの命令を実行します。

遅延スロットの命令が分岐命令であってはなりません。

| 命令符 | |||||||||||||||

| 1 | 0 | 1 | 0 | d | d | d | d | d | d | d | d | d | d | d | d |

|

BRAF Rm |

無条件分岐命令です。

本命令から4バイト後のプログラムカウンタ値にRmの32ビット値を加算する相対分岐です。

本命令は遅延分岐しますので先に遅延スロットの命令を実行します。

遅延スロットの命令が分岐命令であってはなりません。

遅延スロットの命令がRmを変更するものであっても本命令の分岐先は変更前のRmの値で実行されます。

| 命令符 | |||||||||||||||

| 0 | 0 | 0 | 0 | m | m | m | m | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 1 |

|

BSR label |

無条件のサブルーチン呼び出し命令です。 PC の内容を PR に退避してから 本命令から4バイト後のプログラムカウンタ値に符号付の12ビット値を2倍して加算する相対分岐です。 本命令は遅延分岐しますので先に遅延スロットの命令を実行します。遅延スロットの命令が分岐命令であってはなりません。

| 命令符 | |||||||||||||||

| 1 | 0 | 1 | 1 | d | d | d | d | d | d | d | d | d | d | d | d |

|

BSRF Rm |

無条件のサブルーチン呼び出し命令です。

PC

の内容を

PR

に退避してから

本命令から4バイト後のプログラムカウンタ値にRmの32ビット値を加算する相対分岐です。

本命令は遅延分岐しますので先に遅延スロットの命令を実行します。

遅延スロットの命令が分岐命令であってはなりません。

遅延スロットの命令がRmを変更するものであっても本命令の分岐先は変更前のRmの値で実行されます。

| 命令符 | |||||||||||||||

| 0 | 0 | 0 | 0 | m | m | m | m | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 |

|

BT label |

ステータスレジスタのビット T が 1 のときに分岐する命令です。本命令から4バイト後のプログラムカウンタ値に符号付の8ビット値を2倍して加算する相対分岐です。

| 命令符 | |||||||||||||||

| 1 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | d | d | d | d | d | d | d | d |

|

BT/S label |

ステータスレジスタのビット T が

1

のときに分岐する命令です。本命令から4バイト後のプログラムカウンタ値に符号付の8ビット値を2倍して加算する相対分岐です。

本命令は遅延分岐しますので先に遅延スロットの命令を実行します。

遅延スロットの命令が分岐命令であってはなりません。

| 命令符 | |||||||||||||||

| 1 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | d | d | d | d | d | d | d | d |

|

CLRMAC |

MACH、MACL レジスタをクリアします。

| 命令符 | |||||||||||||||

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 |

|

CLRT |

T ビットをクリアします。

| 命令符 | |||||||||||||||

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

|

CMP/EQ Rm,Rn |

汎用レジスタRm とRn とを比較し、 Rn=Rm が成立しているとT ビット をセットします。条件が不成立のときはT ビットをクリアします。

| 命令符 | |||||||||||||||

| 0 | 0 | 1 | 1 | n | n | n | n | m | m | m | m | 0 | 0 | 0 | 0 |

|

CMP/GE Rm,Rn |

汎用レジスタRm とRnの値を符号付き整数として比較し、 Rn≧Rm が成立しているとT ビット をセットします。条件が不成立のときはT ビットをクリアします。

| 命令符 | |||||||||||||||

| 0 | 0 | 1 | 1 | n | n | n | n | m | m | m | m | 0 | 0 | 1 | 1 |

|

CMP/GT Rm,Rn |

汎用レジスタRm とRnの値を符号付き整数として比較し、 Rn > Rm が成立しているとT ビット をセットします。条件が不成立のときはT ビットをクリアします。

| 命令符 | |||||||||||||||

| 0 | 0 | 1 | 1 | n | n | n | n | m | m | m | m | 0 | 1 | 1 | 1 |

|

CMP/HI Rm,Rn |

汎用レジスタRm とRnの値を符号なし整数として比較し、 Rn > Rm が成立しているとT ビット をセットします。条件が不成立のときはT ビットをクリアします。

| 命令符 | |||||||||||||||

| 0 | 0 | 1 | 1 | n | n | n | n | m | m | m | m | 0 | 1 | 1 | 0 |

|

CMP/HS Rm,Rn |

汎用レジスタRm とRnの値を符号なし整数として比較し、 Rn >= Rm が成立しているとT ビット をセットします。条件が不成立のときはT ビットをクリアします。

| 命令符 | |||||||||||||||

| 0 | 0 | 1 | 1 | n | n | n | n | m | m | m | m | 0 | 0 | 1 | 0 |

|

CMP/PL Rn |

汎用レジスタRnの値と0を比較し、 Rn > 0 が成立しているとT ビット をセットします。条件が不成立のときはT ビットをクリアします。

| 命令符 | |||||||||||||||

| 0 | 1 | 0 | 0 | n | n | n | n | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 1 |

|

CMP/PZ Rn |

汎用レジスタRnの値と0を比較し、 Rn >= 0 が成立しているとT ビット をセットします。条件が不成立のときはT ビットをクリアします。

| 命令符 | |||||||||||||||

| 0 | 1 | 0 | 0 | n | n | n | n | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 |

|

CMP/STR Rm,Rn |

汎用レジスタRmとRnに等しいバイトがあったときにT ビット をセットします。

| 命令符 | |||||||||||||||

| 0 | 0 | 1 | 0 | n | n | n | n | m | m | m | m | 1 | 1 | 0 | 0 |