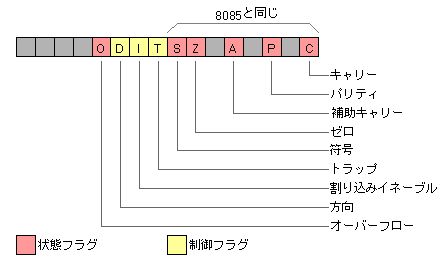

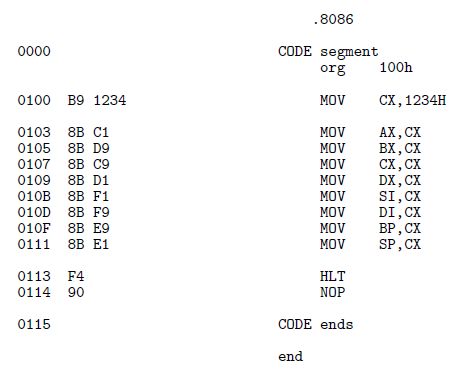

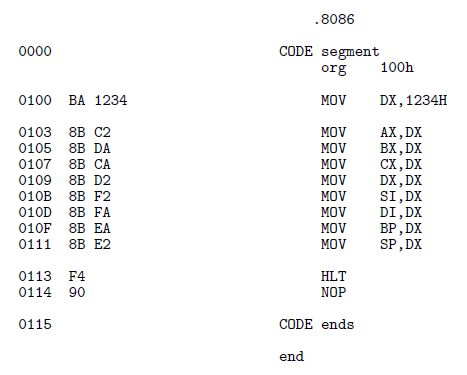

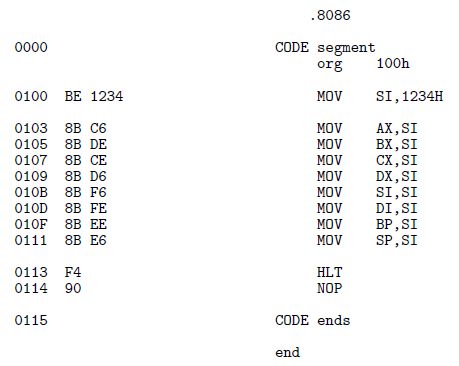

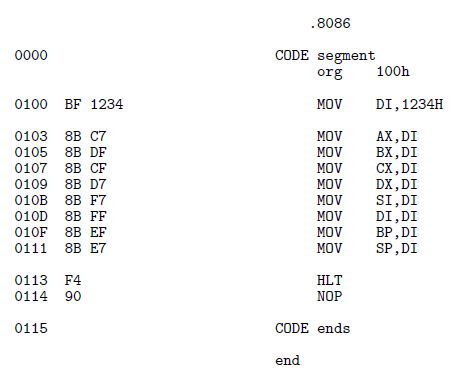

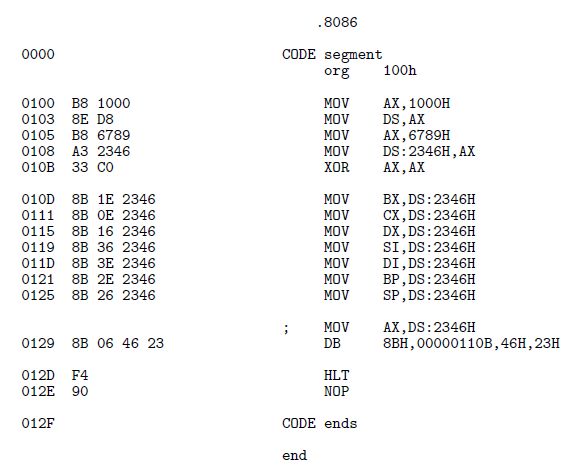

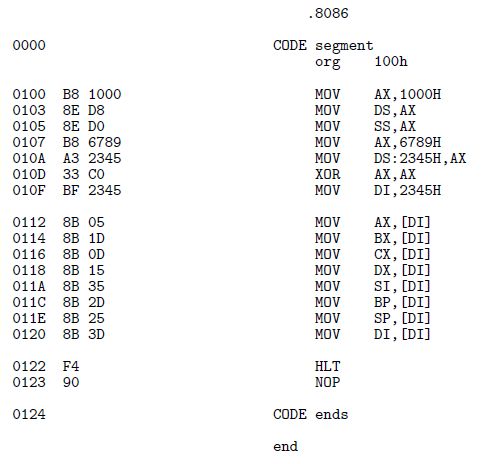

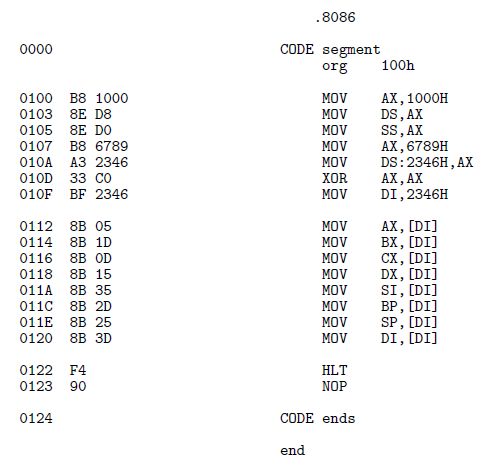

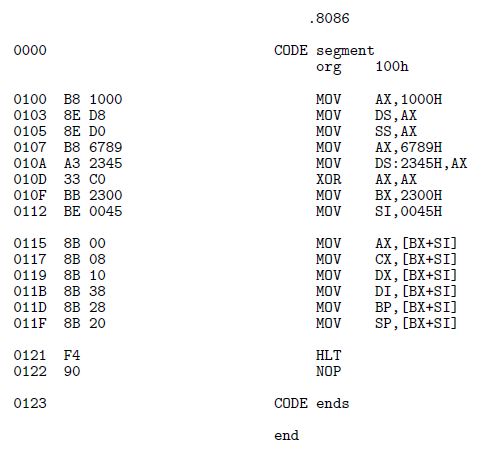

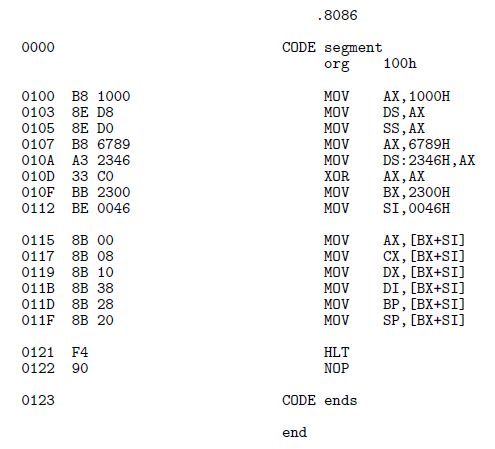

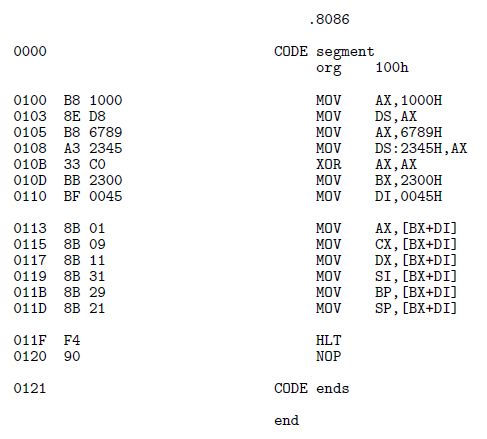

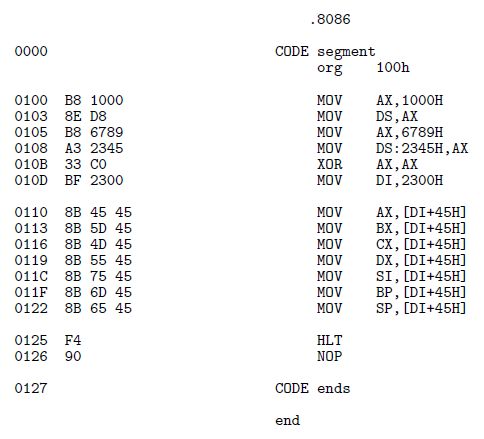

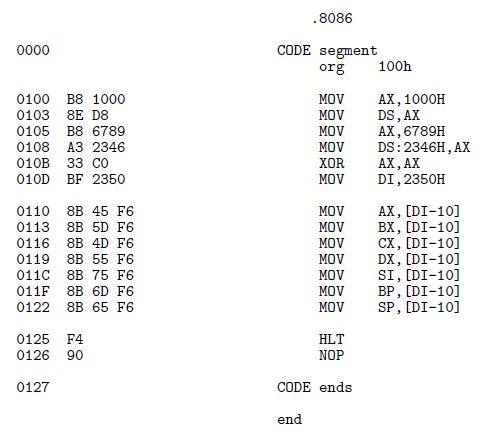

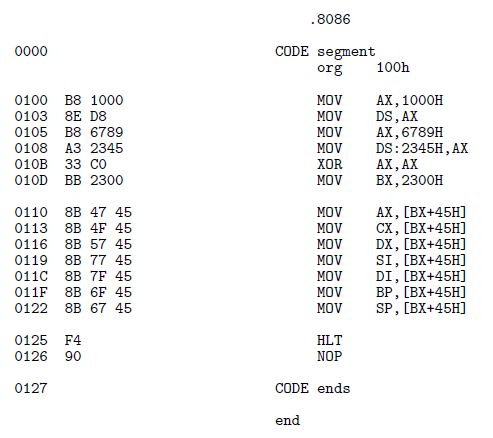

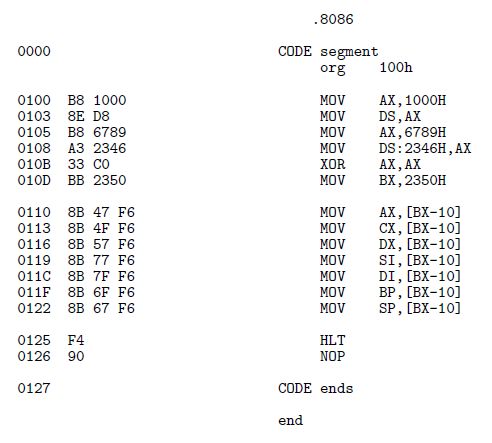

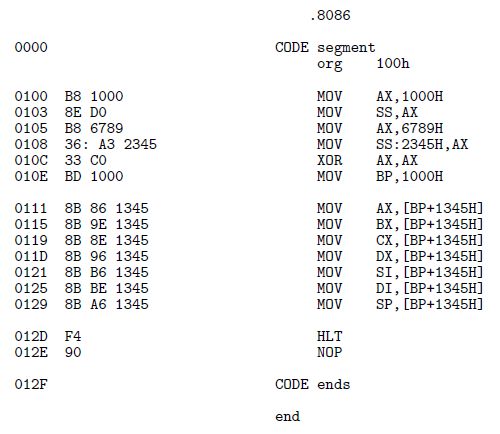

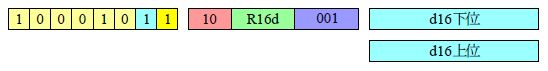

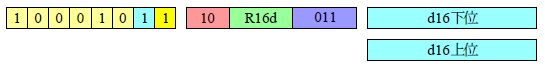

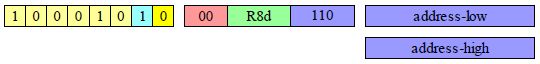

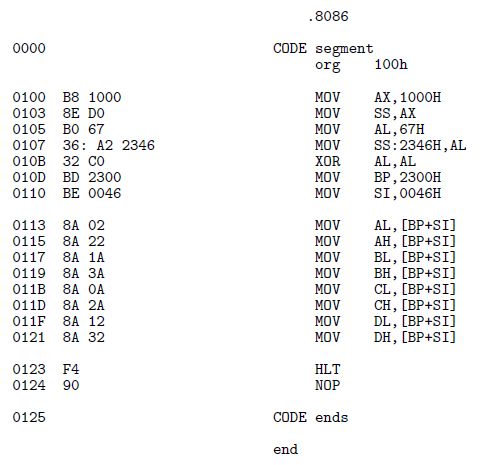

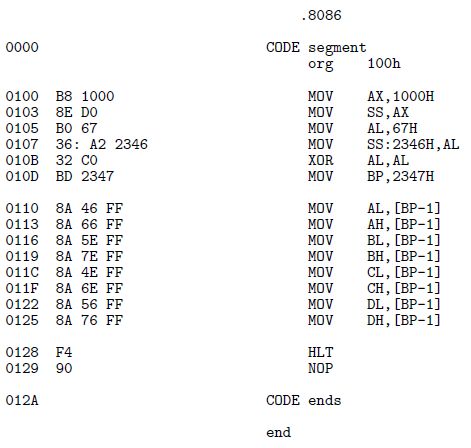

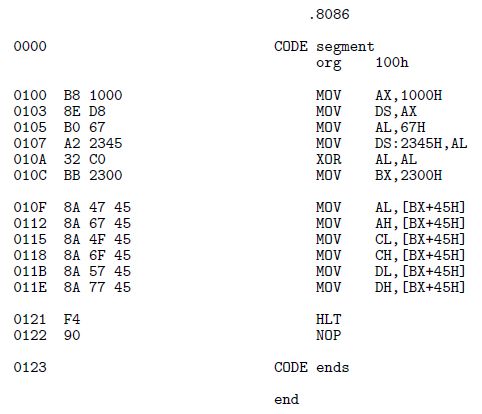

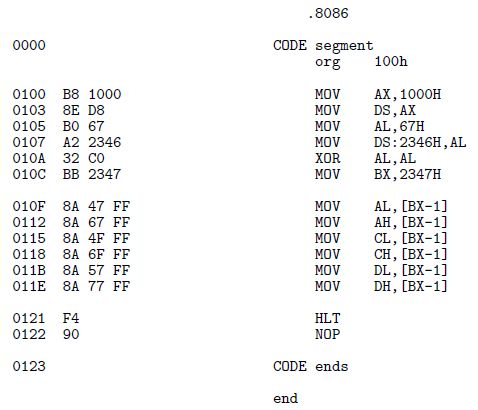

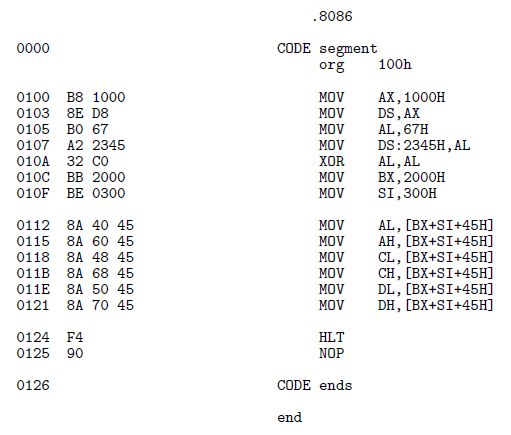

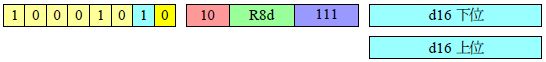

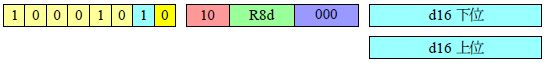

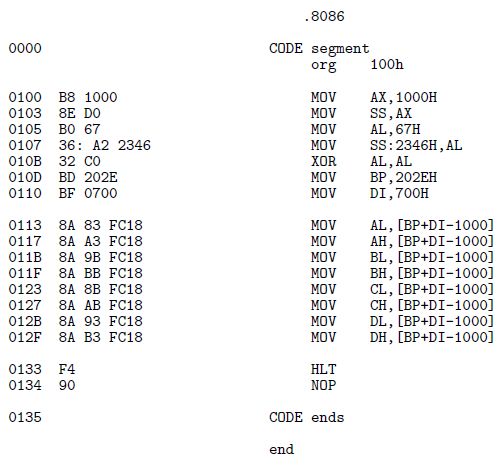

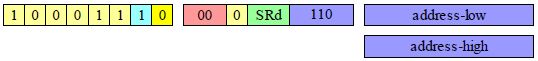

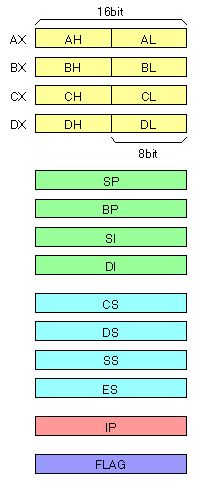

| 図1:レジスタセット |

|

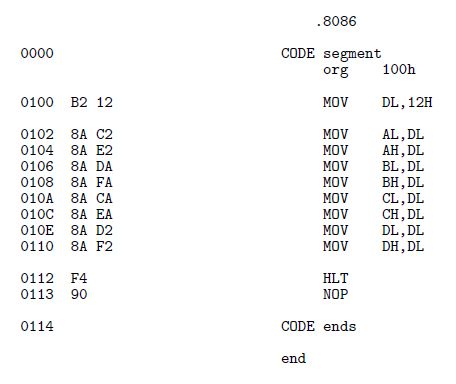

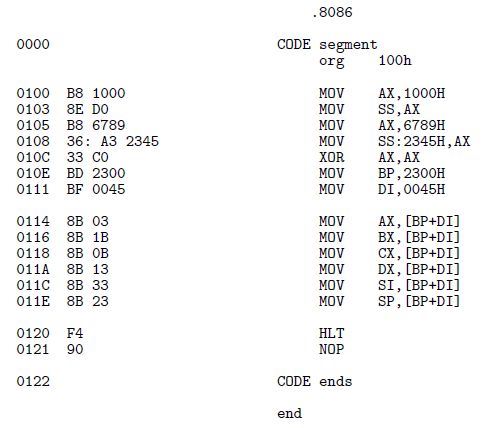

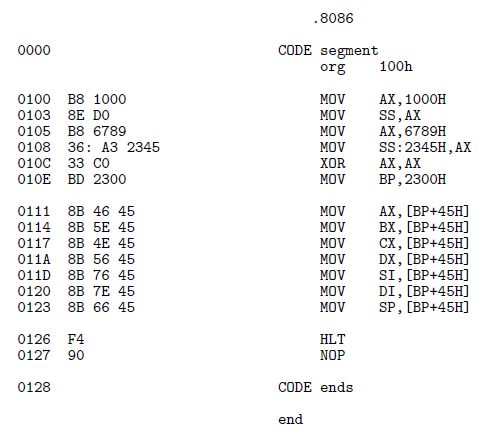

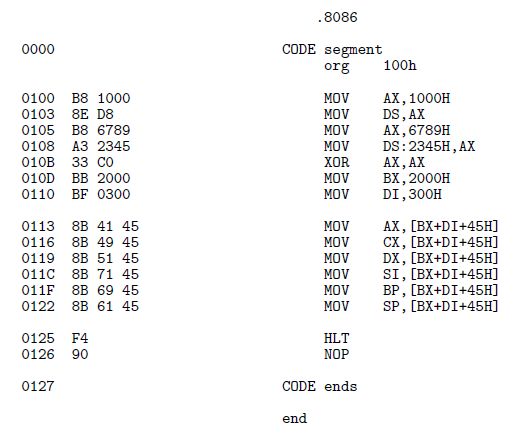

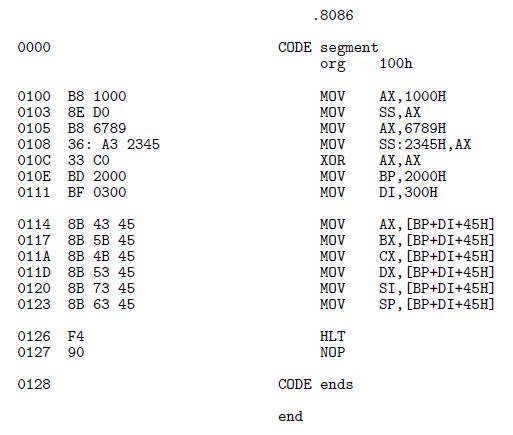

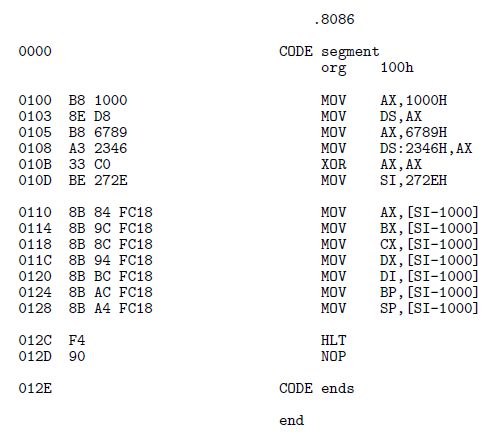

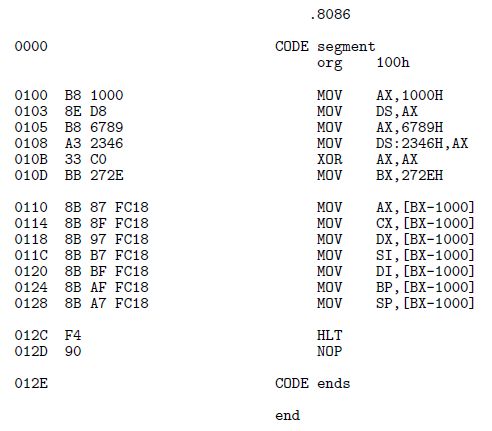

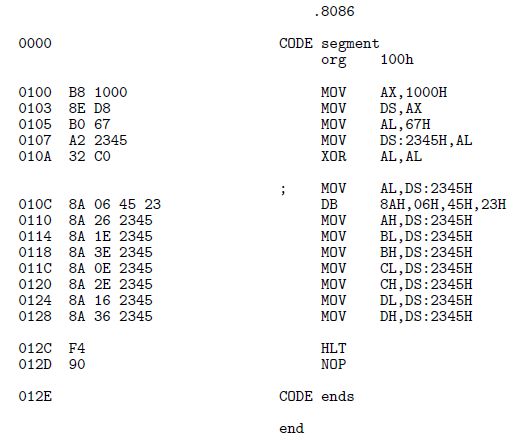

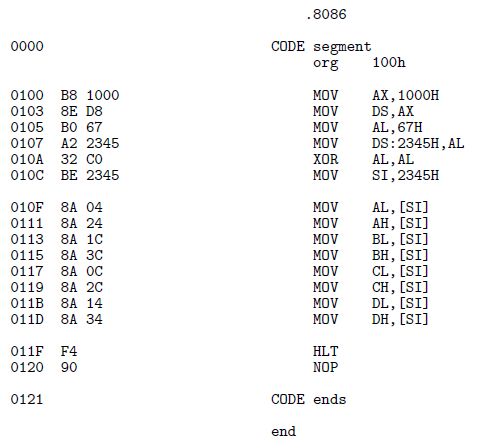

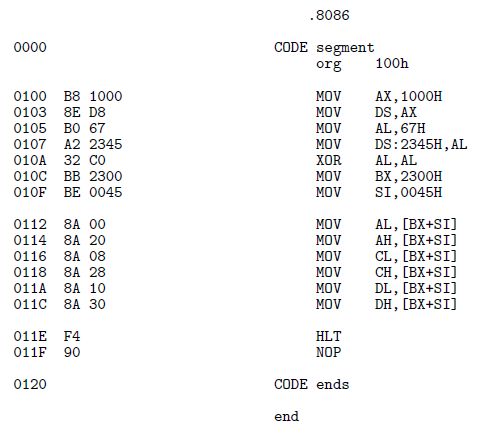

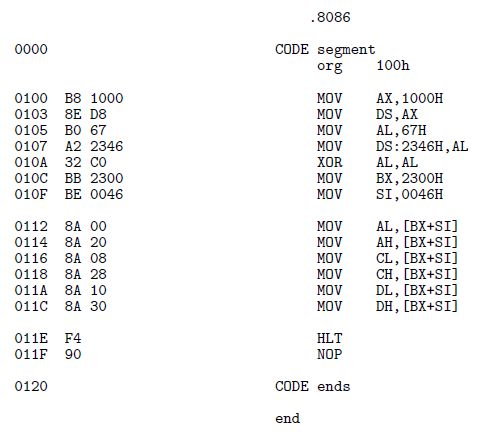

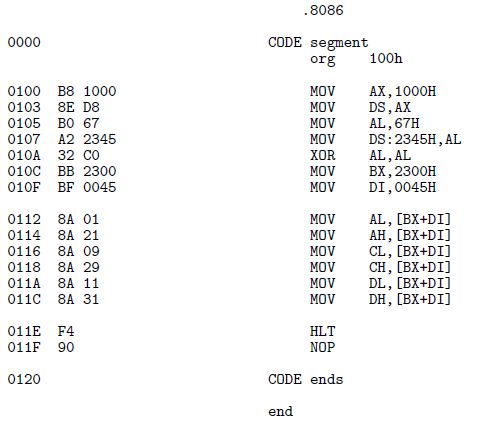

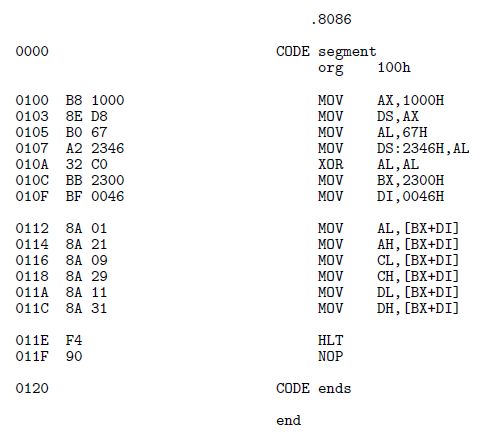

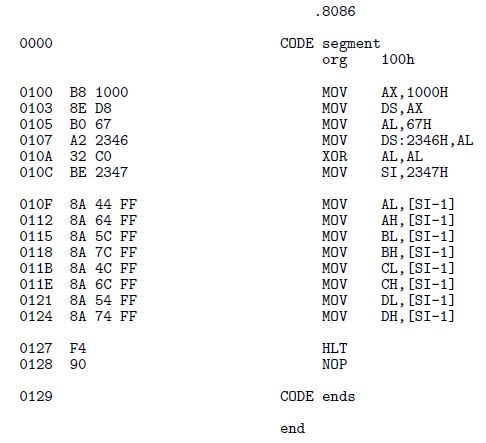

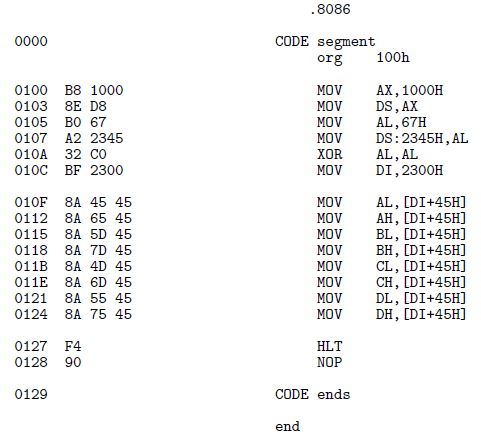

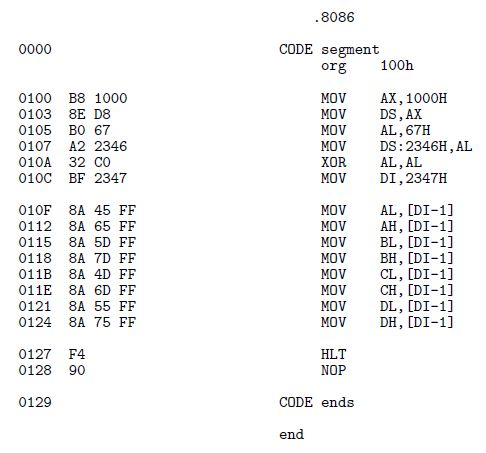

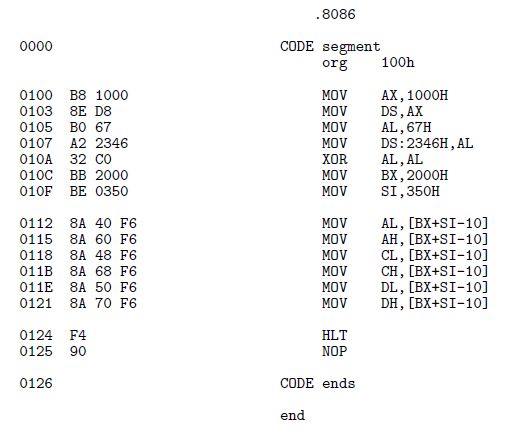

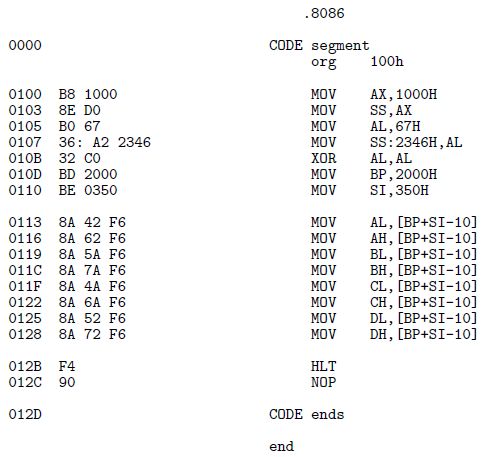

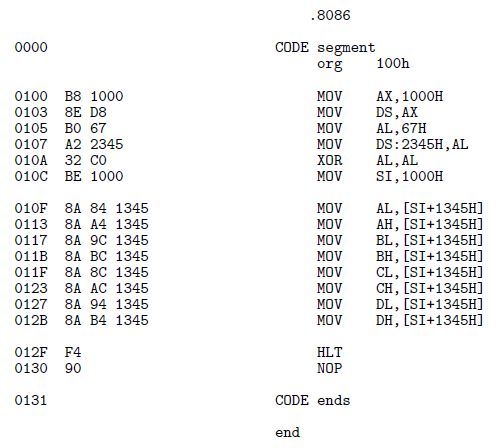

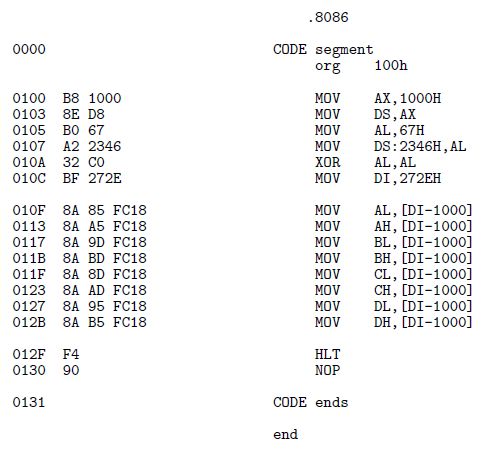

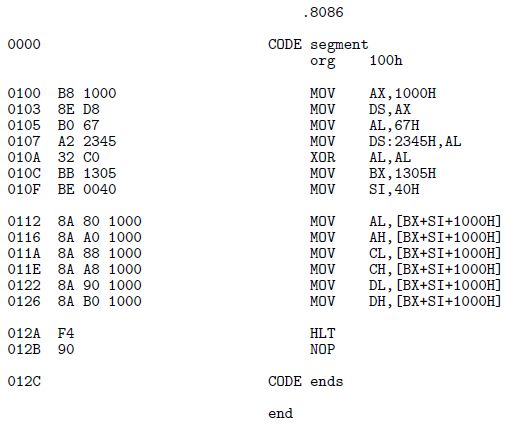

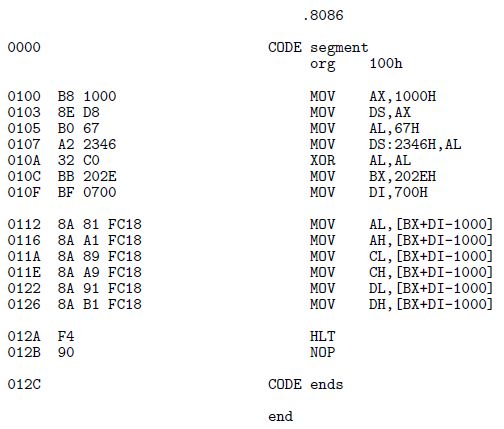

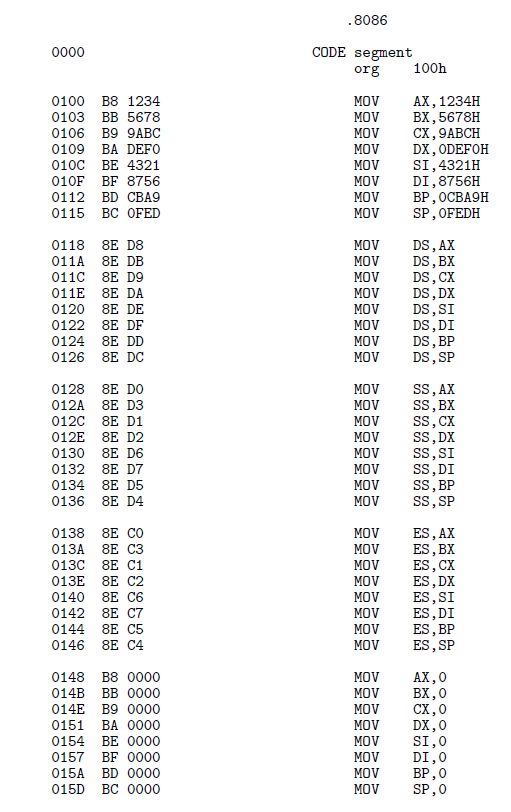

8086のレジスタセットは専用レジスタ形式を採っています。

歴史的にはインテルの最初の16ビットのプロセッサです。

その前には8ビットプロセッサの8085がありますが、これは8080と同じレジスタセットのプロセッサでした。

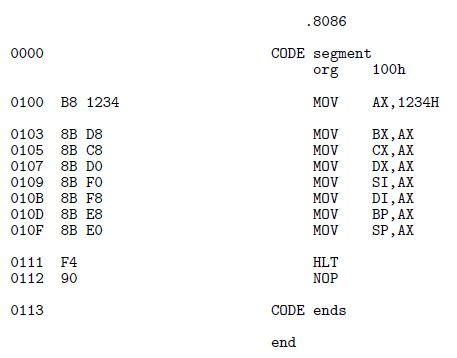

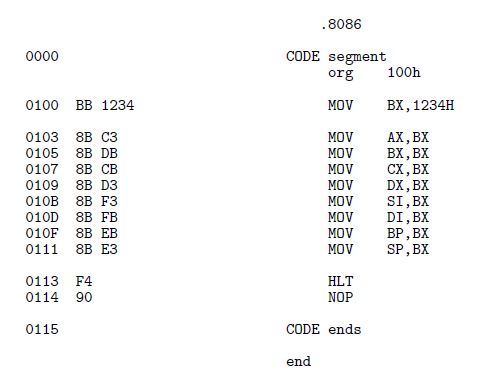

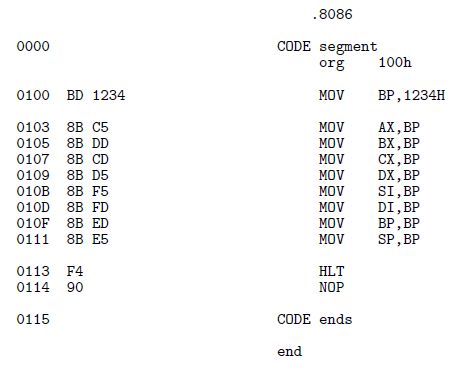

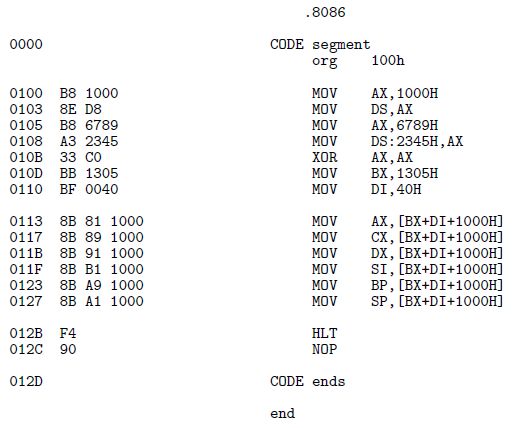

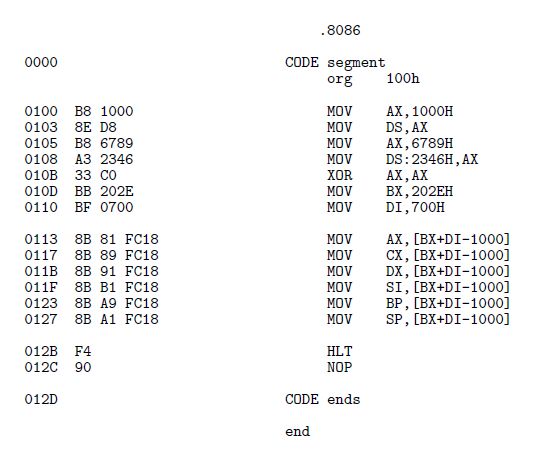

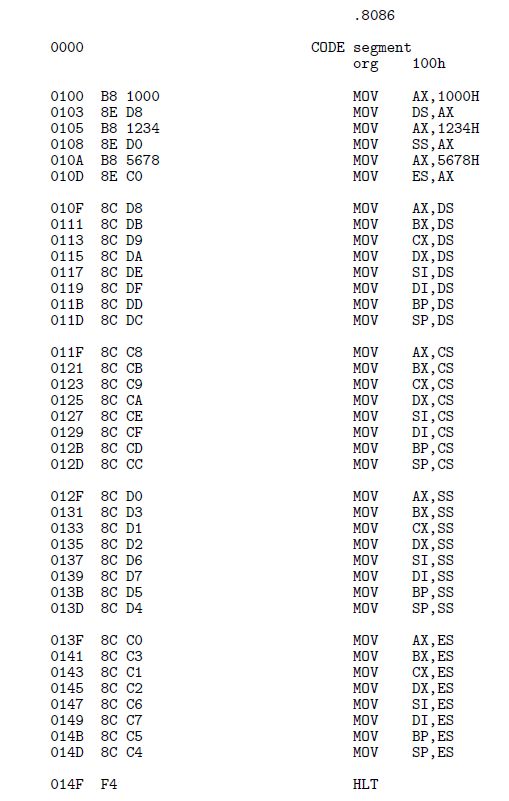

8080はレジスタペアが3本ありましたが、8086のレジスタは

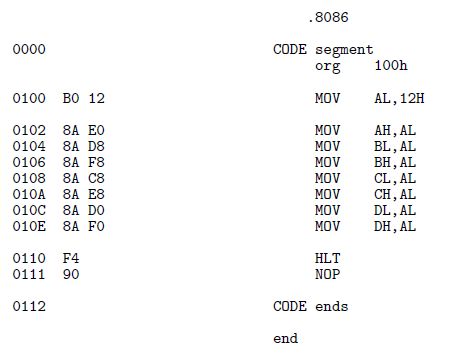

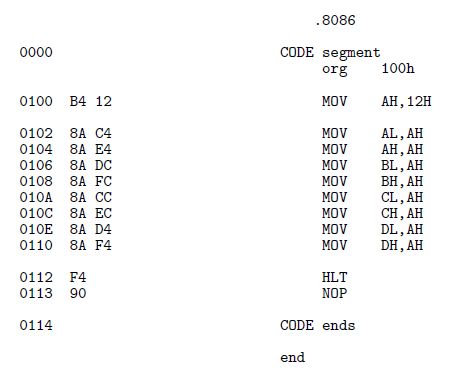

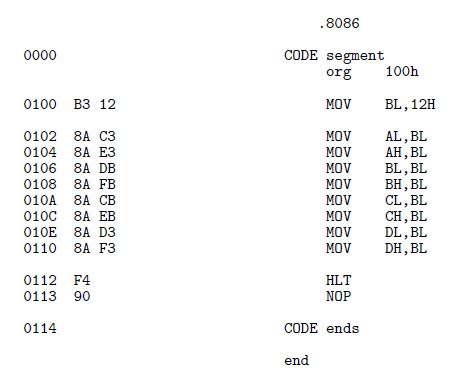

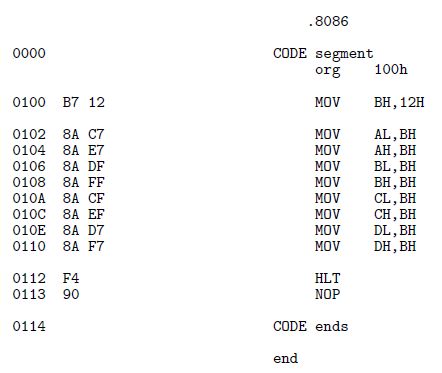

AX,

BX,

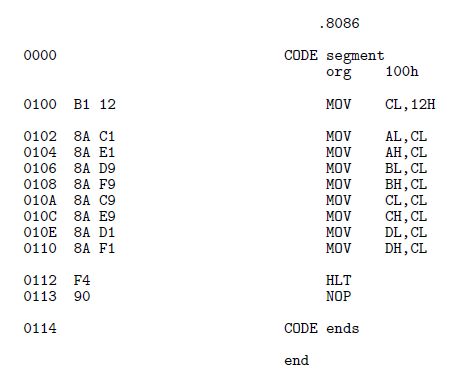

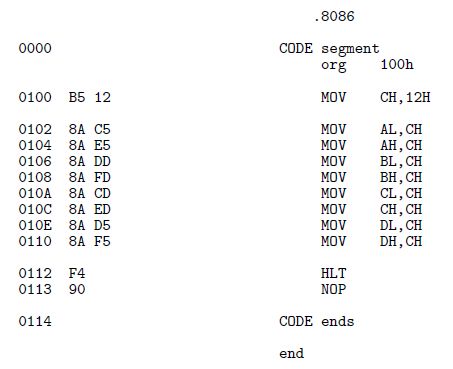

CX,

DX

の4本で上下を8ビットレジスタとして使えますから8080を少し拡張した程度になっています。

これはインテルの8ビットプロセッサのユーザのアセンブラプログラムの変更を容易にすることを考慮したと思われます。

8086で特徴的なのは64Kバイト以上の連続したプログラムやデータを簡単に扱えないことがあります。

8085と同じ40ピンのパッケージに収めることを最優先にしたためにメモリ空間を狭めたことが原因と推測されます。

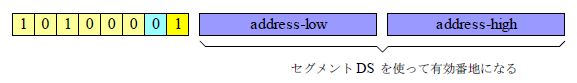

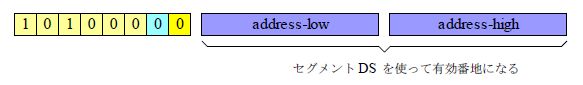

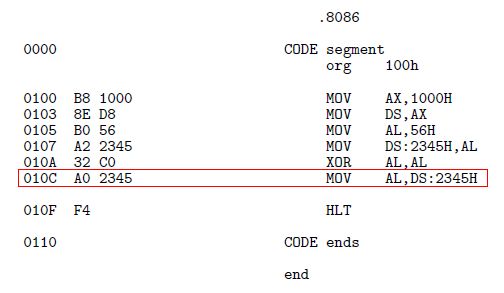

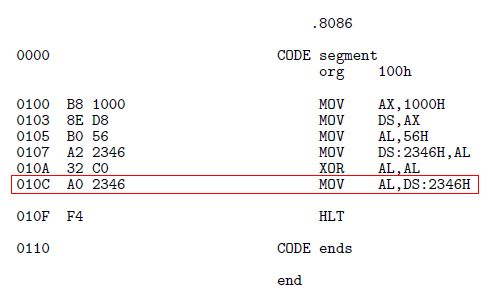

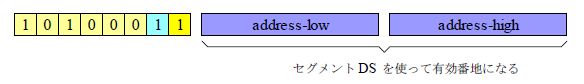

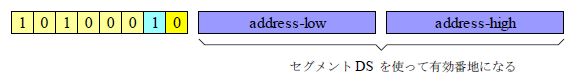

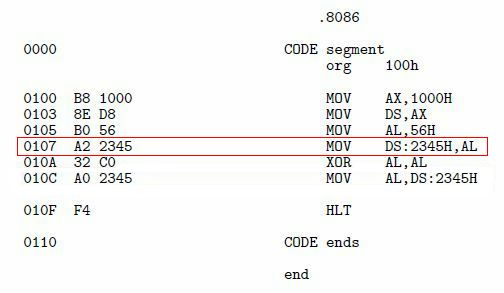

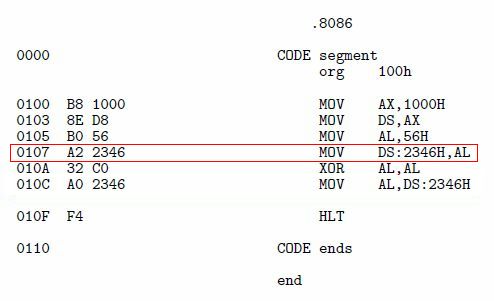

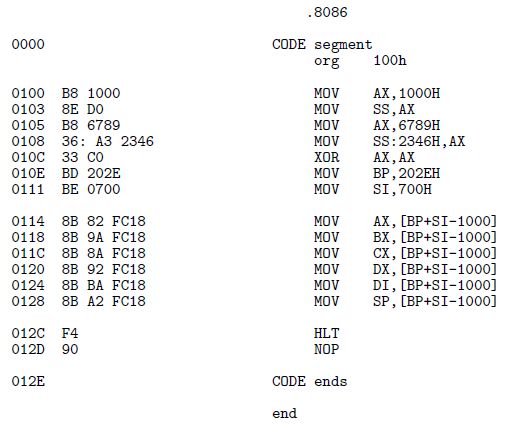

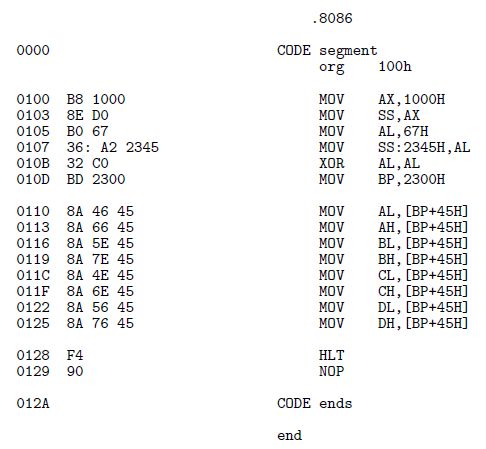

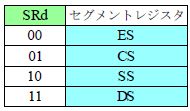

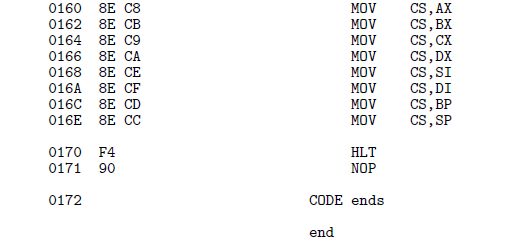

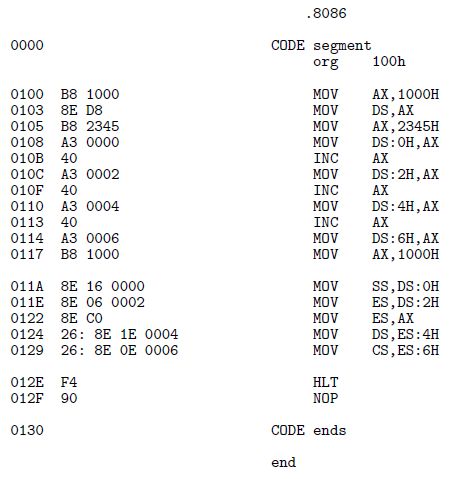

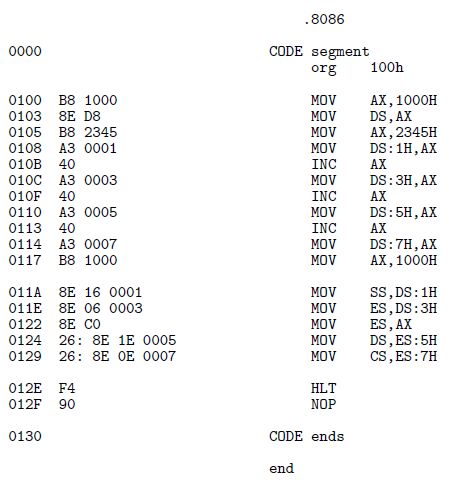

8086はメモリ空間を3種類の専用領域に分割して

CS,

DS,

SS,

ES

の4本のセグメントレジスタに登録します。

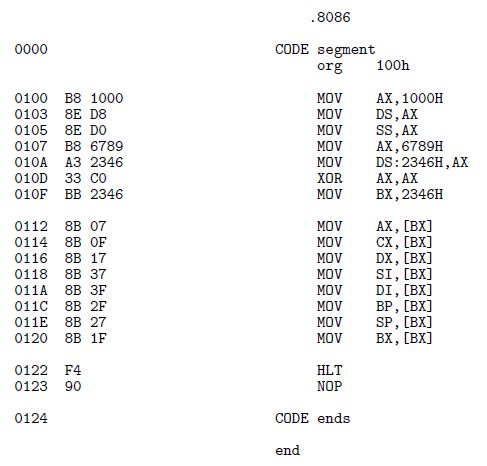

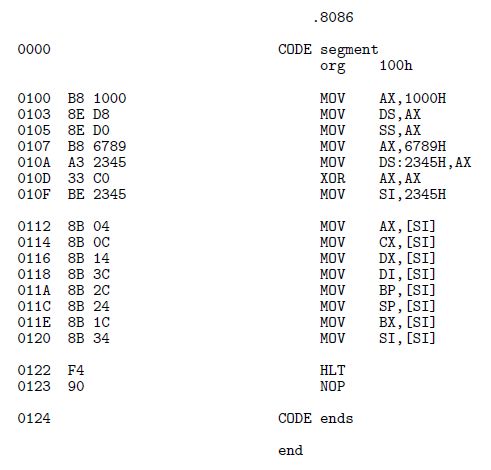

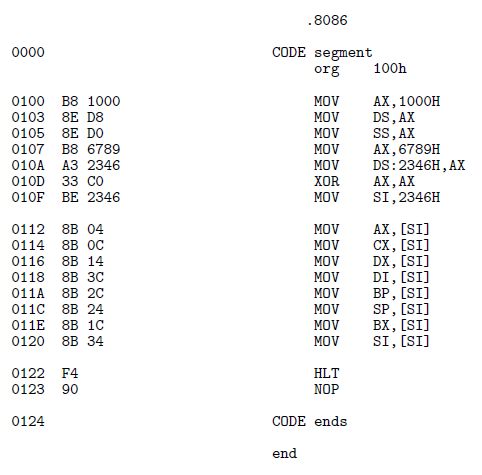

BP,

SI,

DI

の3本のインデックスレジスタを持っていますがセグメント内の相対的な位置を示します、

プログラムカウンタの

IP

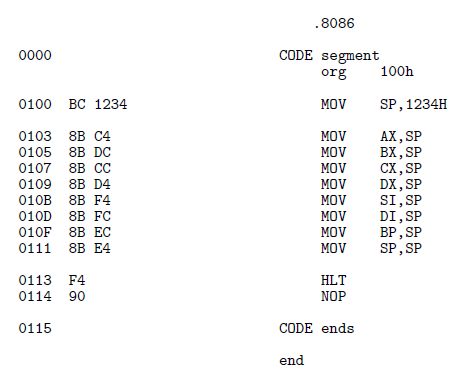

やスタックポインタの

SP

も同様です。