|

Z80について |

|

8080 を拡張した8 ビットのプロセッサでプログラムモデルとして見た場合に8080 用に作られたプログラム も実行できます。演算のほとんどをA レジスタを介して行う専用レジスタの形式を採っています。 |

|

レジスタ |

|

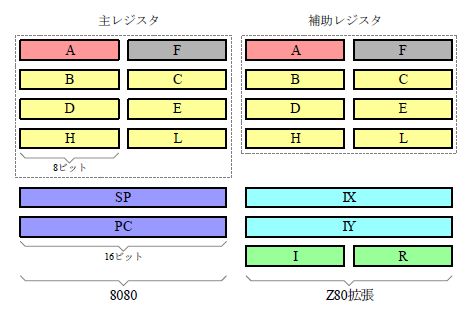

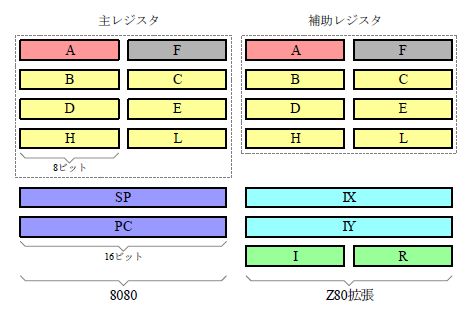

8080 のレジスタを含んで 図1 のように拡張されていますF レジスタはフラグの集まりで通常のレジスタと 異なります。8080 ではレジスタ値をメモリ番地として操作するインデックスレジスタの役割にH とL を連結し たHL レジスタやBC,DE レジスタが使えましたがZ80 ではIX とIY が追加されたのでB,C,D,E,H,L の負担 が軽減されています。補助レジスタの追加によって8 個のレジスタが増えましたがこれは主レジスタと切り替え ながら使用しますので同時には使えません。 |

|

|

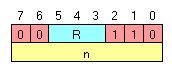

フラグ |

|

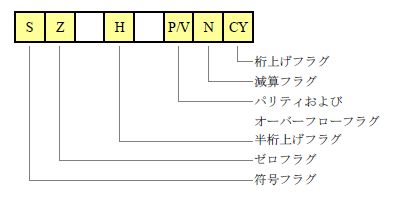

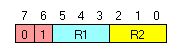

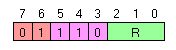

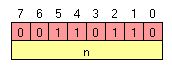

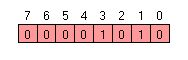

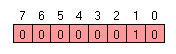

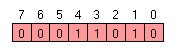

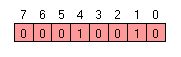

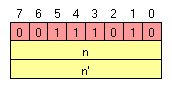

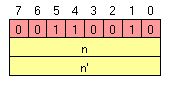

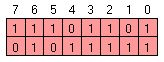

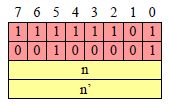

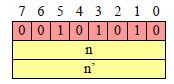

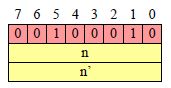

フラグは主に演算結果を記憶しているもので 図2 になります一括して扱う場合はPUSH AF やPOP AF な どの命令がありF レジスタで指定します。 |

|

|

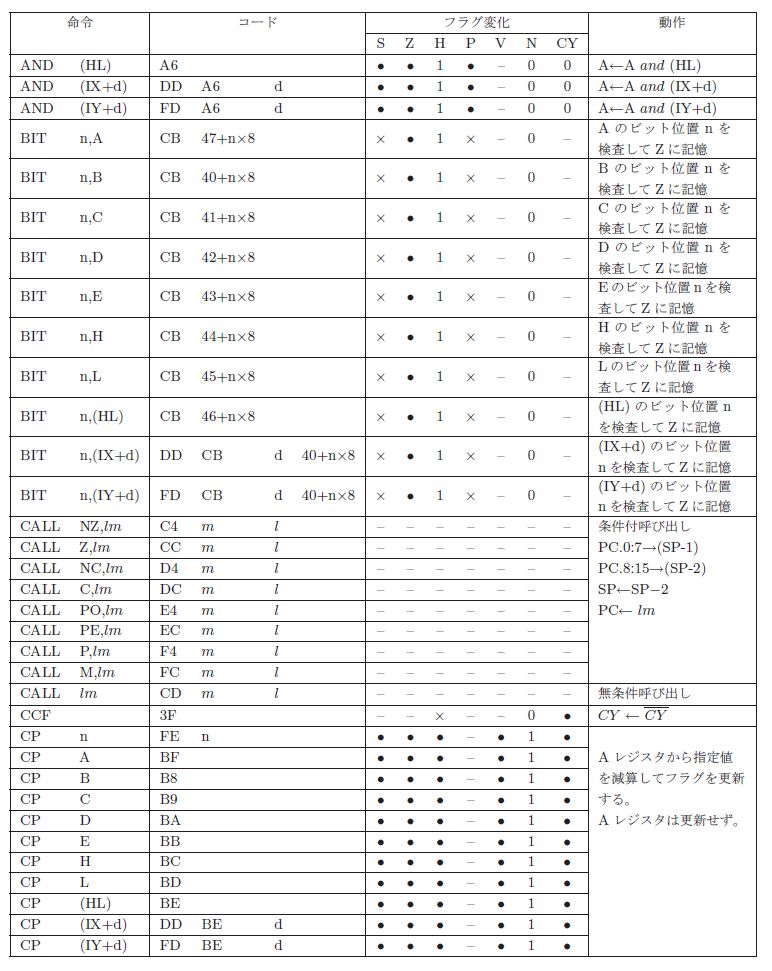

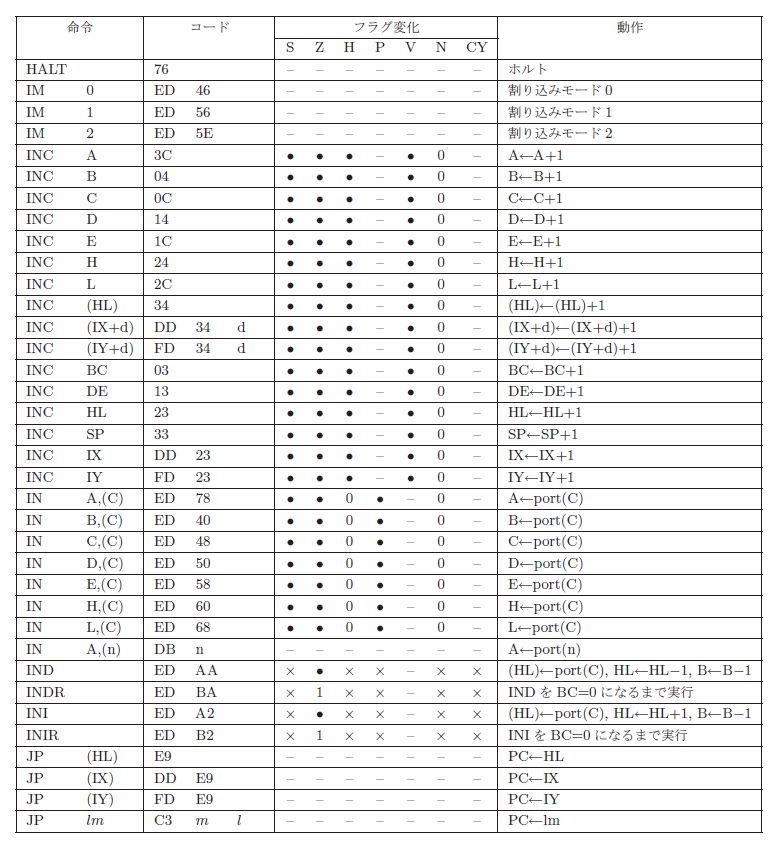

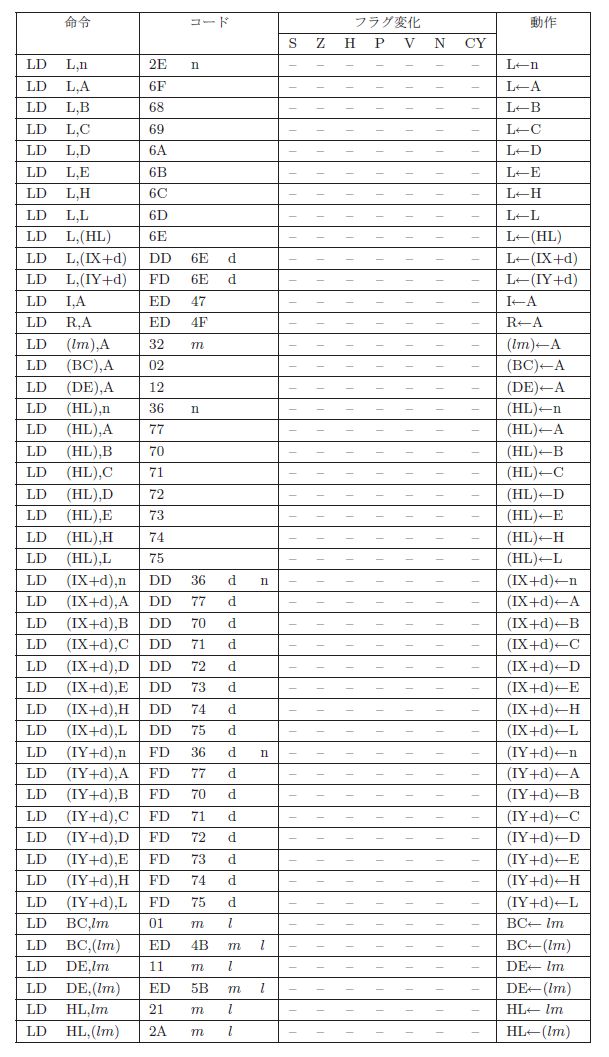

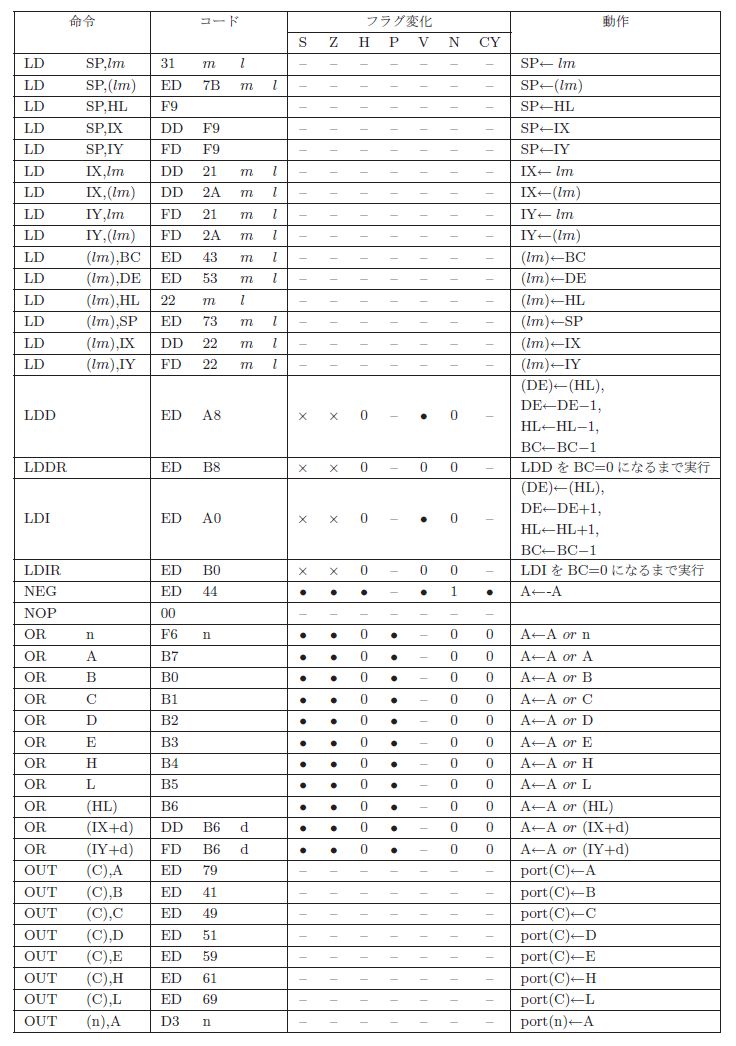

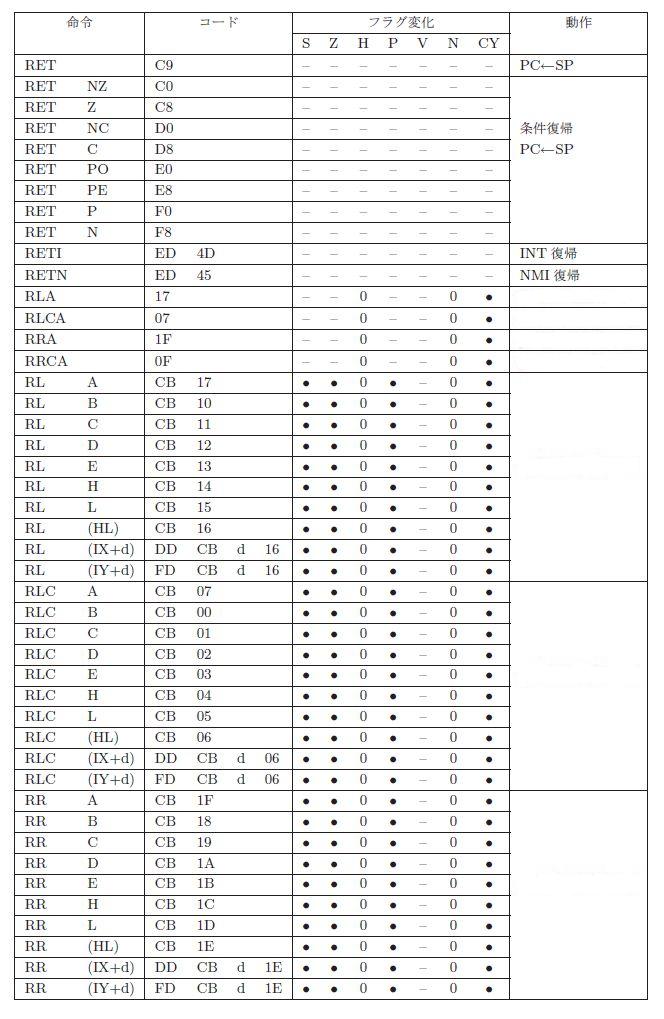

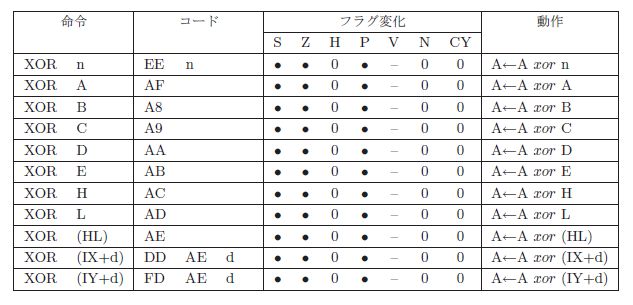

命令表 |

|

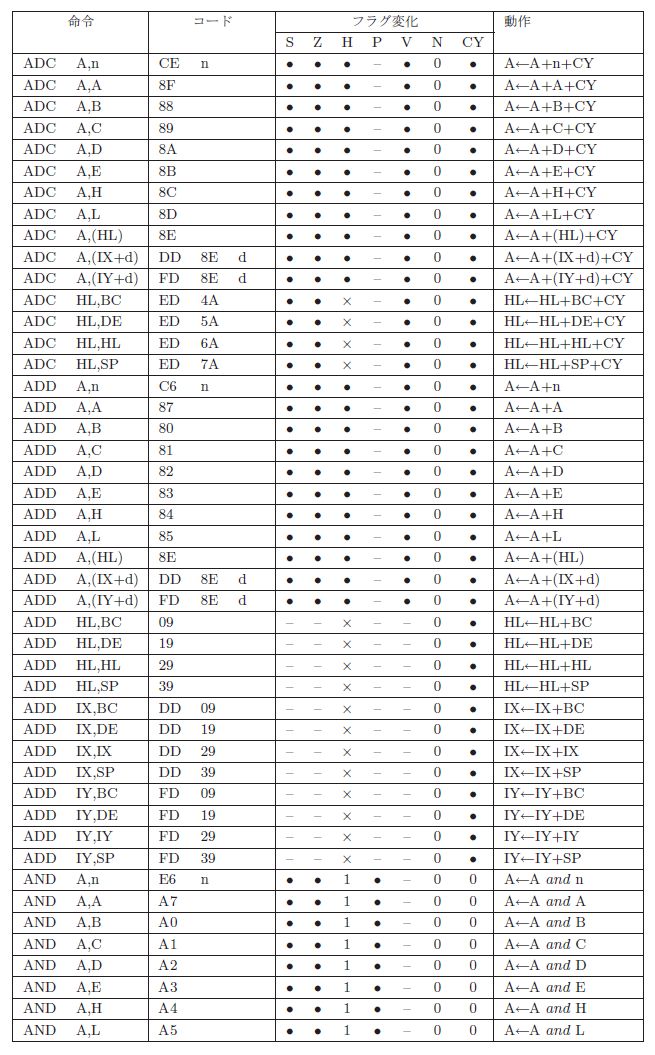

命令は分岐、データ設置、論理演算、算術演算、ビット操作などがありますビット操作は論理演算で代用する ことも可能ですがZ80 では専用の命令が追加されています。命令表の中で使われている記号の意味は次のとお りです。

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

命令符の構造 |

|

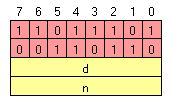

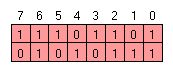

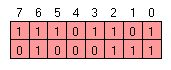

LD R,n |

|

||||||||||||||||||||||||||||||||

|

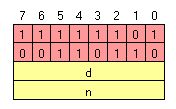

LD R1,R2 |

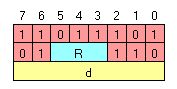

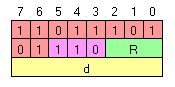

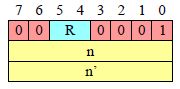

R1とR2の内容は 図10 を参照して下さい。 |

|

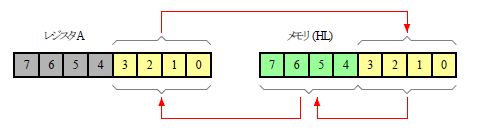

LD R,(HL) |

|

Rの内容は 図10 を参照して下さい。 |

|

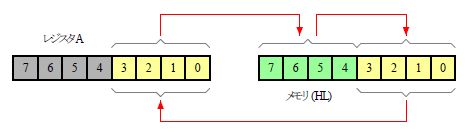

LD (HL),R |

Rの内容は 図10 を参照して下さい。 |

|

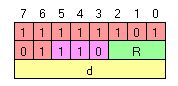

LD R ,(IX+d) |

Rの内容は 図10 を参照して下さい。 |

|

LD (IX+d) ,R |

Rの内容は 図10 を参照して下さい。 |

|

LD R ,(IY+d) |

Rの内容は 図10 を参照して下さい。 |

|

LD (IY+d) ,R |

Rの内容は 図10 を参照して下さい。 |

|

LD (HL) ,n |

|

|

LD (IX+d) ,n |

|

|

LD (IY+d) ,n |

|

|

LD A,(BC) |

|

|

LD (BC),A |

|

|

LD A,(DE) |

|

|

LD (DE) ,A |

|

|

LD A ,(n'n) |

|

|

LD (n'n) ,A |

|

|

LD A ,I |

|

|

LD I ,A |

|

|

LD A ,R |

|

|

LD R ,A |

|

|

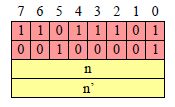

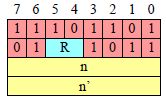

LD RP,n'n |

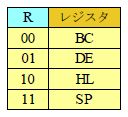

Rの内容は 図14 を参照して下さい。 |

| 図14: レジスタペア選択 |

|

|

LD IX,n'n |

|

|

LD IY,n'n |

|

|

LD HL,(n'n) |

|

|

LD (n'n),HL |

|

|

LD RP,(n'n) |

Rの内容は 図14 を参照して下さい。 |